Introduction

The Vitis™ Application Acceleration Development flow, enables up to 25X better performance/watt for data center application acceleration leveraging FPGAs. Nimbix Inc® has partnered with Xilinx® to deliver an opportunity to test drive Vitis and see how FPGA-based acceleration can speed-up your OpenCL C, C/C++ and RTL Kernels. The Nimbix Cloud provides a purpose-built compute cloud for big data and computation. It now hosts the Vitis development environment for companies who want to streamline evaluations and accelerate FPGA kernels.

Nimbix offers a variety of FPGA resources including the Alveo Accelerator card. See full list of available hardware here: Xilinx FPGAs on Nimbix

Design Examples

A variety of examples are available on the Xilinx GitHub

Hello World

This page will use a simple example to walkthrough the Vitis tools and runtime available on the JARVICE platform which powers the NIMBIX cloud.

Start new Vitis Accel session on JARVICE

- Login to the JARVICE portal for Xilinx

- Review the JARVICE environment:

- JARVICE Runtime Directories

NOTE: Only data in a user's vault is persistent between jobs. NIMBIX recommends using/tmpfor best I/O performance (resulting data must be copied back to your vault before terminating the job). Please refer toJARVICE Runtime Directoriesfor additional information - Transferring Data

- Onboarding

- JARVICE Runtime Directories

-

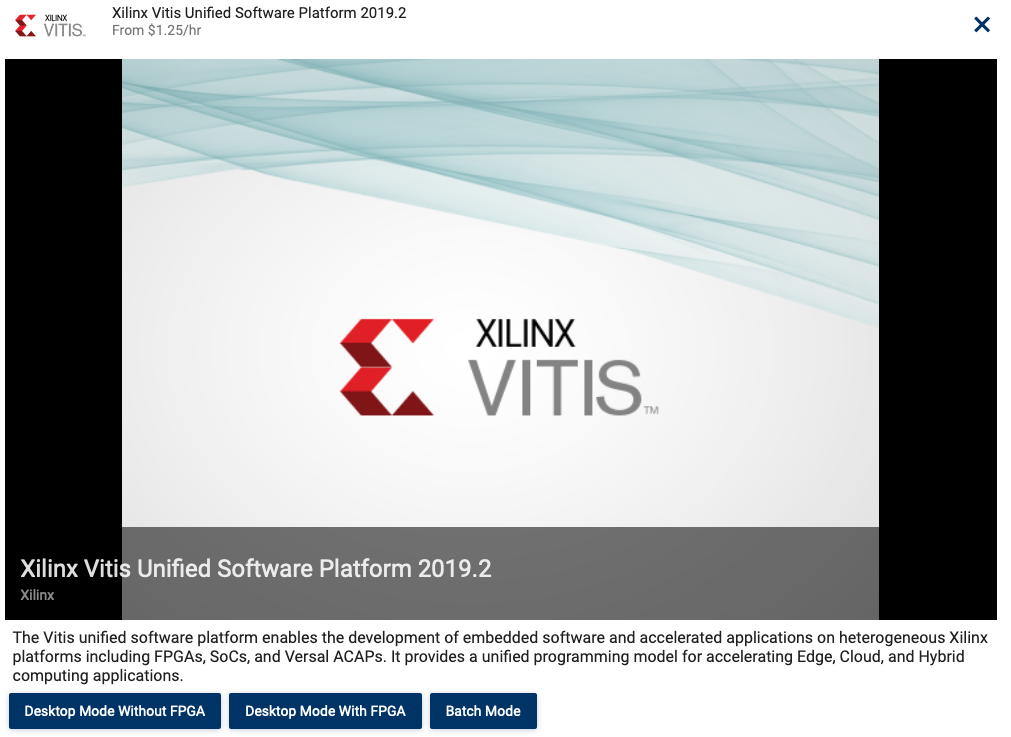

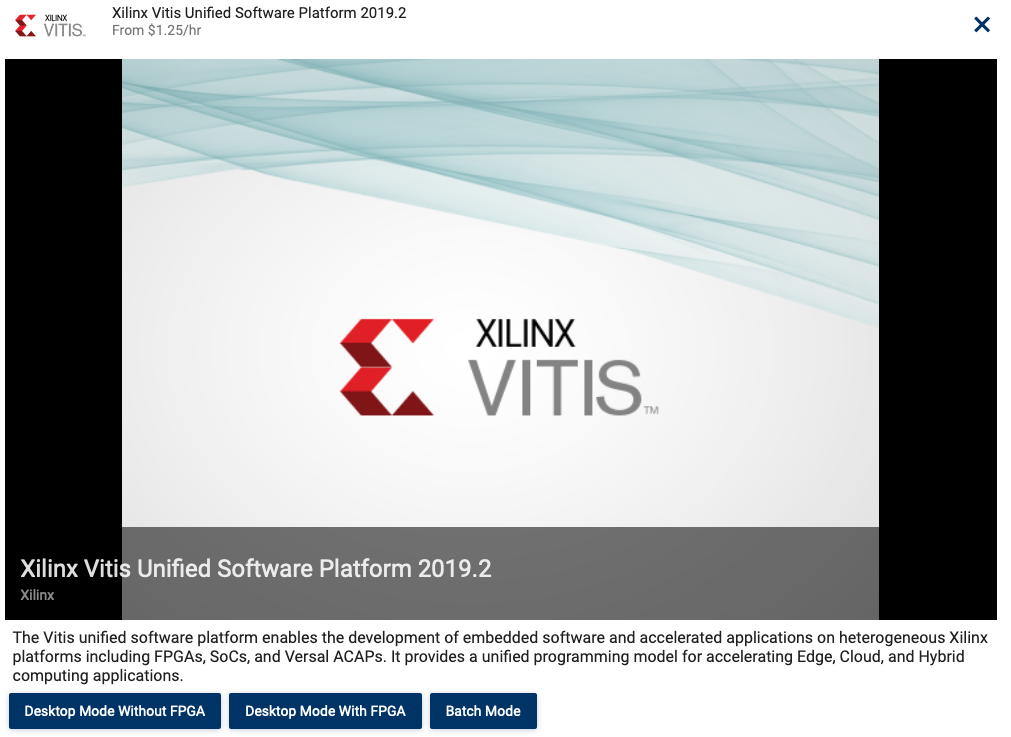

Click on

Xilinx Vitis Unified Software Platform 2019.2application

-

Select the

Desktop Mode Without FPGAoption

-

SUBMITthe job. -

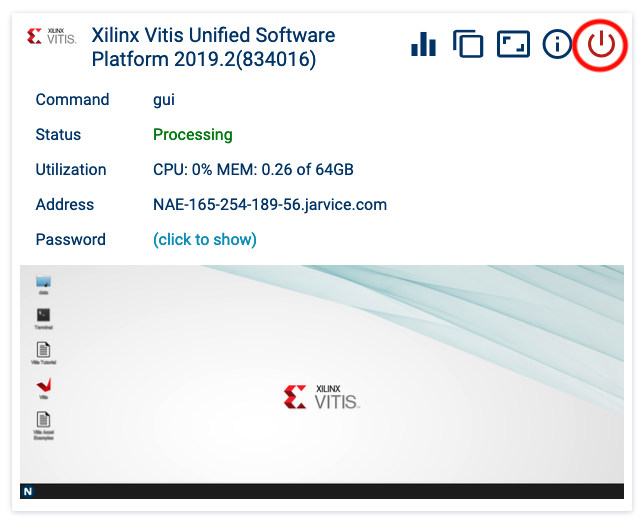

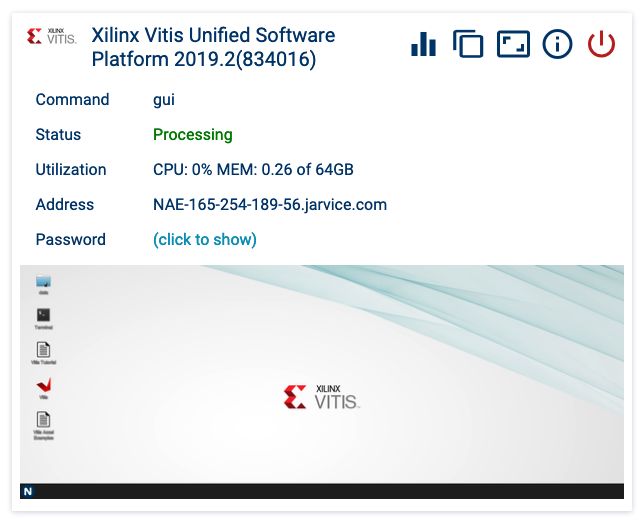

Click on the Desktop Preview to join the Vitis session

Clone Vitis Accel Examples for 2019.2

- Open terminal

- Clone

Hello Worldinto your vault

git clone --depth=1 https://github.com/Xilinx/Vitis_Accel_Examples /data/Vitis_Accel_Examples

Vitis Accel SW emulation

Like most accelerators, there are separate binaries for the host software and accelerated kernel. The Vitis Accel compiler will compile C/C++/VHDL/Verilog source into an *.xclbin binary for the Alveo accelerator card. The compilation process for FPGAs can exceed several hours to create a custom architecture for a design. To alleviate compilation times, Vitis Accel provides a software (sw_emu) and hardware (hw_emu) emulator to test and verify kernel designs. This section will go over using the software emulator.

- Open a terminal

- Compile kernel for sw emulation

# Create local build directory in /tmp

TMP_WORK_DIR=$(mktemp -d)

# Compile for SW emulation

cd /data/Vitis_Accel_Examples/hello_world

make all BUILD_DIR=${TMP_WORK_DIR} TARGET=sw_emu DEVICE=xilinx_u200_xdma_201830_2

Run test with software emulator

# Setup environment for SW emulation

export XCL_EMULATION_MODE=sw_emu

emconfigutil --platform xilinx_u200_xdma_201830_2 --nd 1

# Run emulation test (not on Alveo hardware)

./host ${TMP_WORK_DIR}/vadd.xclbin

Compile for Alveo hardware

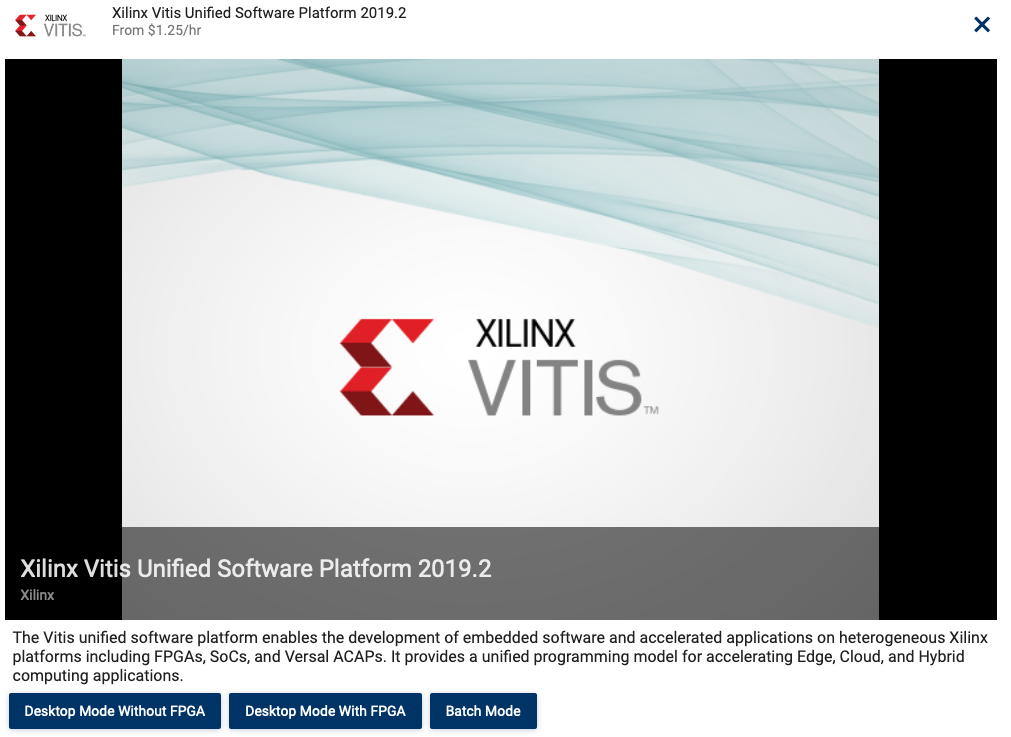

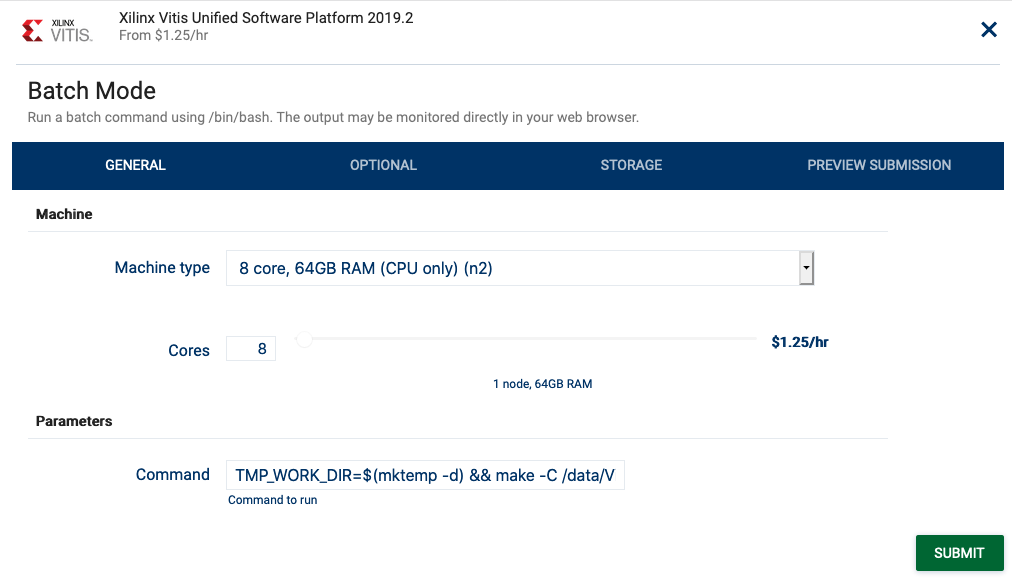

-

Click on

Xilinx Vitis Unified Software Platform 2019.2application

-

Select the

Batch Modeoption

-

Fill in the

Commandbox with:

TMP_WORK_DIR=$(mktemp -d) && make -C /data/Vitis_Accel_Examples/hello_world all BUILD_DIR=${TMP_WORK_DIR} TARGET=hw DEVICE=xilinx_u200_xdma_201830_2 && cp ${TMP_WORK_DIR}/*.xclbin /data/Vitis_Accel_Examples/hello_world

A batch (non-interactive) job will start on the JARVICE Dashboard to build the Hello World *.xclbin file. This job will shutdown after completion. The *.xclbin file will be saved in the vault at /data/Vitis_Accel_Examples/hello_world

NOTE Ensure data is being written to the vault /data when using batch/non-interactive jobs. All other data (e.g. written to ${HOME}) will be lost when the job ends.

Run Hello World on Alveo

-

Click on

Xilinx Vitis Unified Software Platform 2019.2application

-

Select the

Desktop Mode With FPGAoption

-

Open terminal and run

Hello World

# List available Xilinx accelerators

xbutil list

# Get general info

xbutil query

# Run Hello World

cd /data/Vitis_Accel_Examples/hello_world

./host vadd.xclbin

Shutdown Vitis Accel